Суммирующий счетчик работает по принципу суммирования сигналов, поступающих на его вход (см. таблицу 3.3.3.1). На рисунке 3.3.3.1 приведена функциональная схема трехразрядного суммирующего счетчика и временная диаграмма работы (см. рисунок 3.3.3.2), в таблице 3.3.3.1 – состояния его триггеров(Тг). В начальный момент времени все триггеры устанавливаются сигналом Уст 0 в состояние “0”. После прихода первого счетного импульса триггер Тг1 перейдет в состояние “1” и в счетчике зафиксируется код 001.Второй импульс, пришедший на вход, переведет Тг1 снова в состояние “0”. При этом возникает импульс переноса, который устанавливает следующий триггер Тг2 в состояние “1” и в счетчике зафиксируется код 010. После третьего входного сигнала Тг1 вновь прейдет в состояние “1”, а остальные триггеры останутся в прежнем состоянии. Так будет продолжаться до тех пор, пока счетчик не просуммирует максимальное для трех разрядов число 710=1112. Восьмой импульс переведет Тг1 в состояние “02, возникший перенос поступит на Тг2 и также переведет его в состояние “0”. В свою очередь, импульс переноса со второго разряда переведет в состояние “0” и Тг3. В результате этого счетчик установится в исходное нулевое состояние (000)

Счетчики обратного счета (вычитающие счетчики).

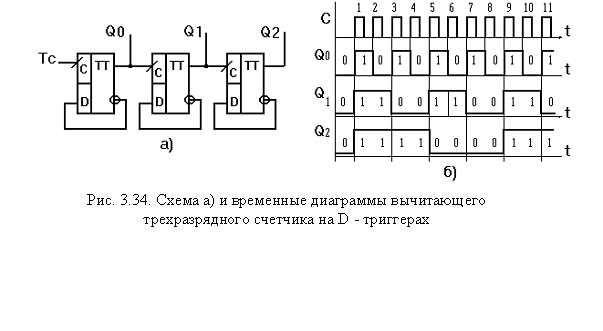

На рис. 3.34 приведена схема асинхронного трехразрядного двоичного вычитающего счетчика, построенного на базе D-триггеров. Отметим, что условия для изменения состояний триггеров вычитающих счетчиков аналогичны условиям для суммирующих счетчиков с той лишь разницей, что они должны “опираться” на значения инверсных, а не прямых выходов триггеров. Следовательно, рассмотренный выше счетчик можно превратить в вычитающий, просто переключив входы “С” триггеров с выходов Q на выходы . Когда в качестве разрядных триггеров используются D-триггеры, синхронизируемые передним фронтом синхроимпульсов, для получения вычитающего счетчика (асинхронного) входы “С” последующих тригеров соединяются с прямыми выходами предыдущих, также как в счетчике прямого счета, построенного на JK-триггерах.

Работа вычитающего счетчика на D-триггерах наглядно иллюстрирована на рис. 3.34, (б). Из рис. 3.34 следует, что после нулевого состояния всех триггеров, с приходом первого синхроимпульса они устанавливаются в состояние “1”. Поступление второго синхроимпульса приводит к уменьшению этого числа на одну единицу и т.д. После поступления восьмого импульса, снова, все триггеры обнуляются и цикл счета повторяется, что соответствует модулю М=8.

Счетчики, которые в процессе работы могут менять направление счета называются реверсивными.

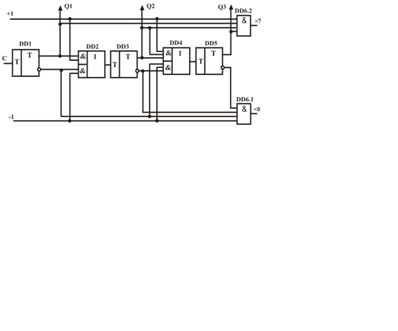

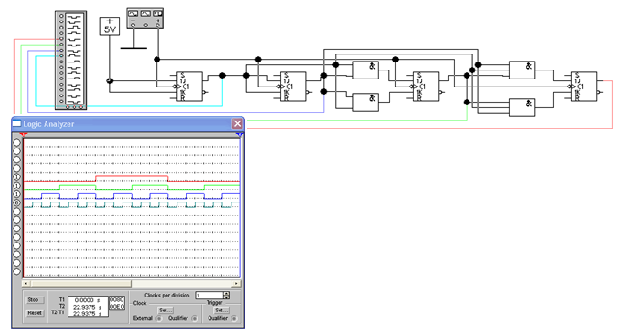

Для счетных импульсов предусмотрены два входа: "+1" - на увеличение, "-1" - на уменьшение. Соответствующий вход (+1 или -1) подключается ко входу С. Это можно сделать схемой ИЛИ, если влепить ее перед первым триггером (выход элемента ко входу первого триггера, входы - к шинам +1 и -1). Непонятная фигня между триггерами (DD2 и DD4) называется элементом И-ИЛИ. Этот элемент составлен из двух элементов И и одного элемента ИЛИ, объединенных в одном корпусе. Сначала входные сигналы на этом элементе логически перемножаются, потом результат логически складывается.

Число входов элемента И-ИЛИ соответствует номеру разряда, т. е. если третий разряд, то три входа, четвертый - четыре и т. д. Логическая схема является двухпозиционным переключателем, управляемым прямым или инверсным выходом предыдущего триггера. При лог. 1 на прямом выходе счетчик отсчитывает импульсы с шины "+1" (если они, конечно, поступает), при лог. 1 на инверсном выходе - с шины "-1". Элементы И (DD6.1 и DD6.2) формируют сигналы переноса. На выходе >7 сигнал формируется при коде 111 (число 7) и наличии тактового импульса на шине +1, на выходе <0 сигнал формируется при коде 000 и наличии тактового импульса на шине -1.